Pethau i'w Hystyried Wrth Ddylunio Bwrdd USB

Apr 06, 2022

Yn y dyluniad USB2.0, mae'r gwahaniaeth USB D plws /D- yn gweithio yn y modd cyflym o 480Mbps, a gall cloc y system weithio ar 12 MHz, 48 MHz a 60 MHz. Mae'n perthyn i'r rhan dylunio cyflym yn y dyluniad caledwedd. Mae yna lawer o agweddau sydd angen sylw arbennig. Oherwydd bod ceblau USB yn tueddu i ffurfio antenâu monopole, rhaid atal cerrynt RF rhag cyplu i'r cebl.

D plws / D-: Signal gwahaniaethol cyflym, sy'n cael ei ymyrryd yn hawdd gan sŵn allanol ac sy'n effeithio ar ansawdd trosglwyddo'r signal.

Signal cyflenwad pŵer VBUS: Bydd y crychdonni cyflenwad pŵer ar y pin signal cyflenwad pŵer yn achosi ymyrraeth fawr i'r signal trosglwyddo data, felly rhaid ei hidlo. A dylid hidlo'r signal daear hefyd i leihau ymyrraeth. Hefyd yn talu sylw i foltedd sag ar gyfer llwythi cyfredol uchel.

D plws /D- rheolaeth hyd cyfartal: Wrth weithio mewn modd cyflym iawn neu gyfradd USB3.0, mae angen sicrhau gwifrau D plws /D- hyd cyfartal. D plws a D – ni ddylai olion fod yn wahanol o fwy na 50 mils (1.25 mm) o hyd er mwyn osgoi gogwydd signal ac atal effeithiau foltedd AC

D plws a D – dylai olion fod yn llai na 3 modfedd (75 mm) o hyd. Argymhellir na ddylai hyd y ddau olion fod yn fwy nag 1 fodfedd

Wrth lwybro, dylai'r ongl sgwâr gael ei phlygu ddwywaith ar 45 gradd neu ei dalgrynnu (yn lle ongl sgwâr o 90 gradd)

Rheoli rhwystriant: D plws / D- gwifrau gwahaniaethol, rheolaeth rhwystriant 90Ω ± 10 y cant

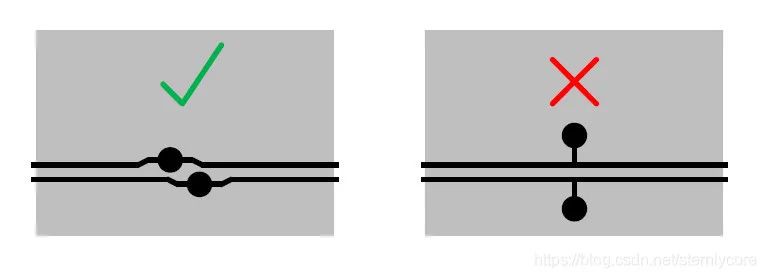

Dim Stub (dim ffwlcrwm): Wrth ychwanegu pwyntiau prawf neu rai dyfeisiau, ceisiwch sicrhau nad oes gan y signal gwahaniaethol unrhyw ffwlcrwm, fel y dangosir isod:

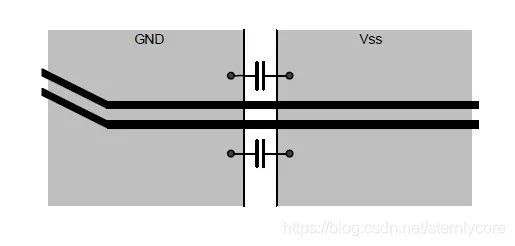

Plân cyfeirio cyflawn: Mae gweithredu rhwystriant D plws /D yn gofyn am awyren gyfeirio gyflawn, ni all unrhyw awyrennau cyfeirio hollt ddigwydd. Os na chaiff planau cyfeirio ar wahân ymddangos, mae angen cysylltu cynwysyddion siwmper, fel y dangosir isod:

Nawr mae'r integreiddio sglodion yn uchel iawn, ac mae dyluniad ymylol USB_Host yn gymharol syml, fel y dangosir isod:

Dyfais sy'n cyfyngu ar y cerrynt: RT9702, mae llwyth safonol USB2.0 yn gofyn am uchafswm cerrynt o 500mA o VBUS, a bydd yn cael ei ddiffodd os yw'n fwy na 500mA

Amddiffyniad electrostatig: Mae SRV05 yn atal trydan statig rhag niweidio'r signal cysylltydd, a'i osod yn agos at y rhyngwyneb USB

Gleiniau magnetig L1 / L2: Dileu sŵn amledd uchel ar signalau pŵer a gwella perfformiad gwrth-jitter. Mae gwerth gwrthiant y gleiniau magnetig rhwng 47ohm a 1000ohm (ar amlder signal 100MHz), wedi'i osod yn agos at y cysylltydd

R157/R158: Cydweddu gwrthyddion i atal gorlenwi signal, mae'r gwrthiant yn gyffredinol rhwng 10Ω-33Ω, wedi'i osod yn agos at y rheolydd USB

CP1: Mae'r cynhwysydd mawr yn sicrhau bod y foltedd VBUS yn gostwng yn ormodol ar hyn o bryd o blygio a dad-blygio neu pan fydd llawer iawn o ddata'n cael ei drosglwyddo, ac fe'i gosodir yn agos at y rhyngwyneb USB.